Slide 1 - Design and Analysis of a 1.8V to 1.2V Low Dropout Regulator (LDO)

Design and Analysis of a 1.8V to 1.2V Low Dropout Regulator (LDO)

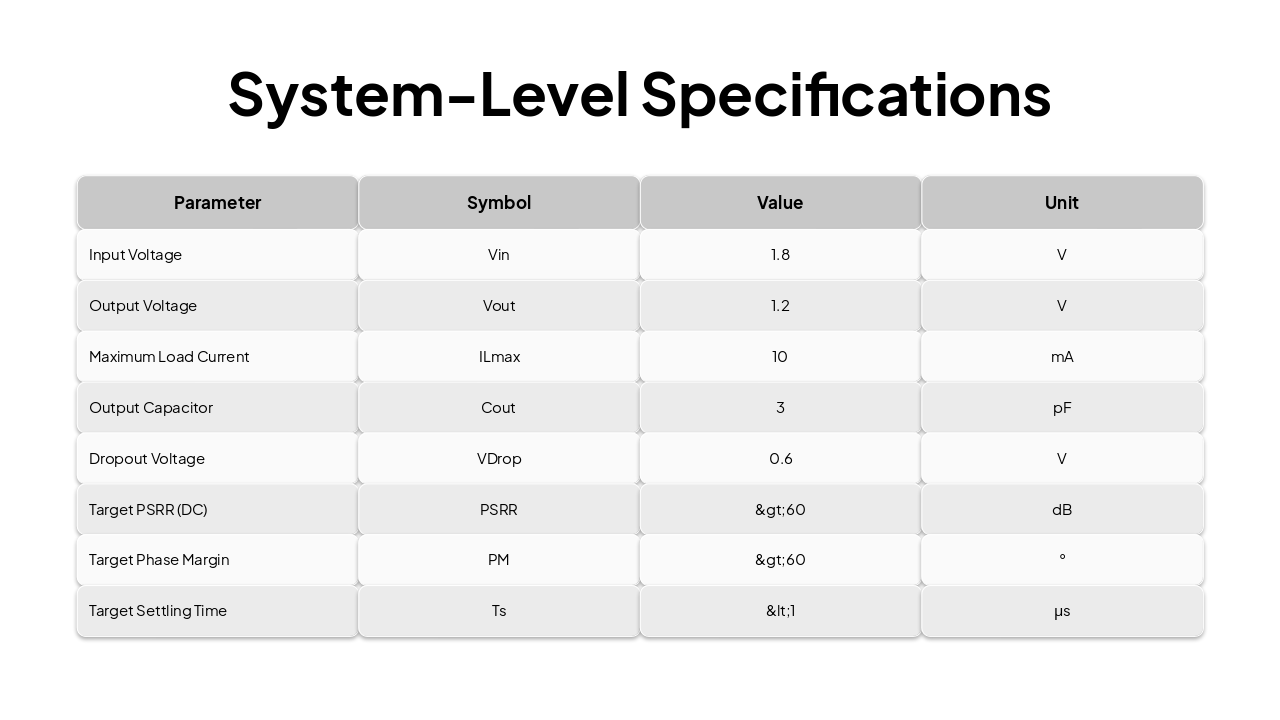

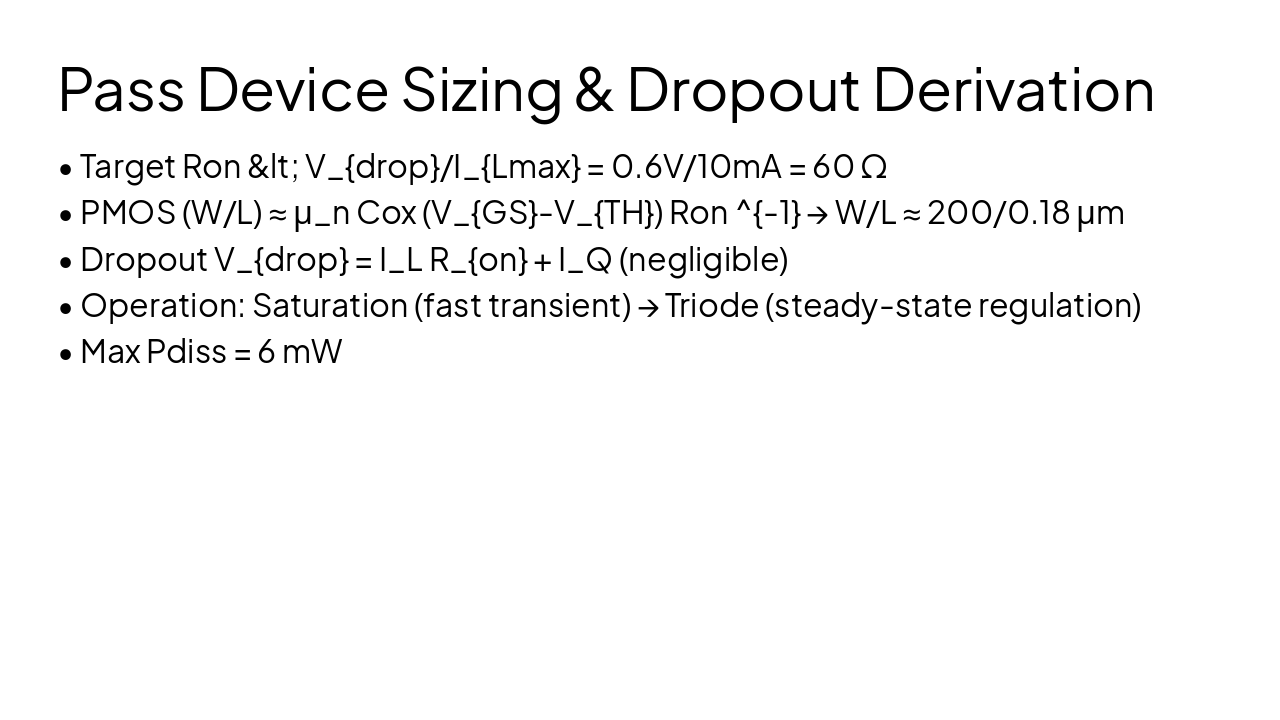

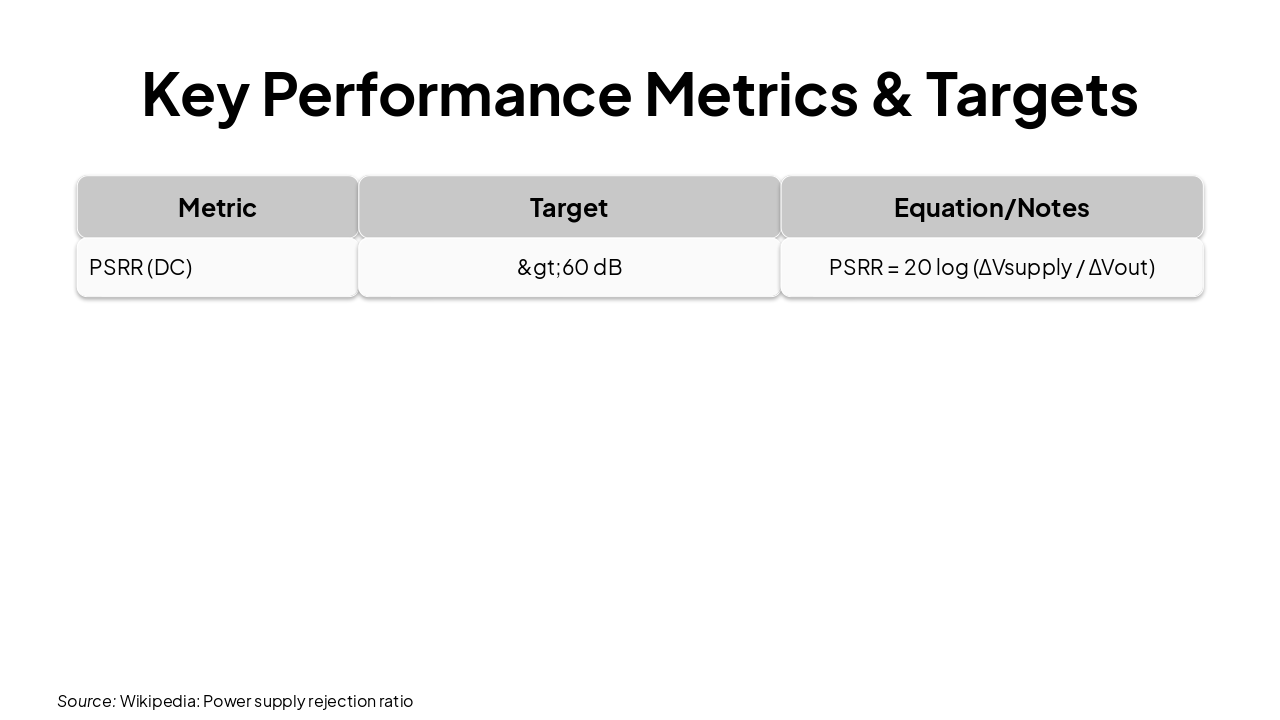

Vin = 1.8V, Vout = 1.2V, Imax = 10mA, Cout = 3pF PhD/Industry Technical Review

---

Photo by Umberto on Unsplash